### Freescale Semiconductor Product Brief Advance Information

# **MSC8122**

### Quad Core 16-Bit Digital Signal Processor

The raw processing power of this highly integrated systemon- a-chip device will enable developers to create nextgeneration networking products that offer tremendous channel densities while maintaining system flexibility, scalability, and upgradeability. The MSC8122 is offered in three core speed levels: 300, 400, and 500 MHz.

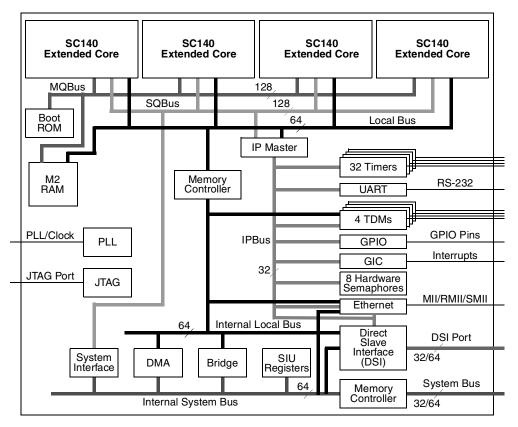

Figure 1. MSC8122 Block Diagram

The MSC8122 is a highly integrated system-on-a-chip that combines four SC140 extended cores with an RS-232 serial interface, four time-division multiplexed (TDM) serial interfaces, thirty-two general-purpose timers, a flexible system interface unit (SIU), an Ethernet interface, and a multi-channel DMA engine. The four extended cores can deliver a total 4800/6400/8000 DSP MMACS performance at 300/400/500 MHz.

Each core has four arithmetic logic units (ALUs), internal memory, a write buffer, and two interrupt controllers. The MSC8122 targets high-bandwidth highly computational DSP applications and is optimized for wireless transcoding and packet telephony as well as high-bandwidth base station applications. The MSC8122 delivers enhanced performance while maintaining low power dissipation and greatly reduces system cost.

Note: This document contains information on a new product. Specifications and information herein are subject to change without notice.

© Freescale Semiconductor, Inc., 2004, 2005. All rights reserved.

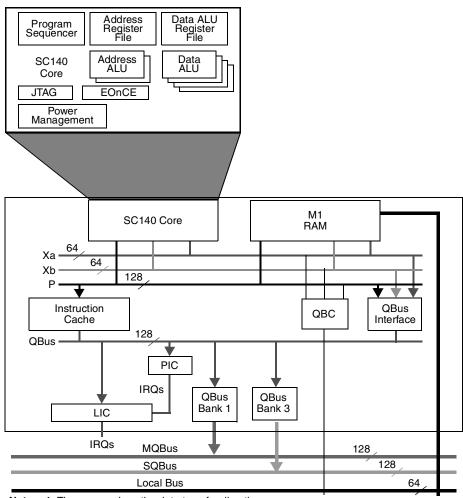

Notes: 1. The arrows show the data transfer direction.

2. The QBus interface includes a bus switch, write buffer, fetch unit, and a control unit that defines four QBus banks. In addition, the QBC handles internal memory contentions.

### **Features**

| Feature     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SC140 Cores | <ul> <li>Four SC140 cores:</li> <li>Up to 8000 MMACS using 16 ALUs running at up to 500 MHz.</li> <li>A total of 1436 KB of internal SRAM (224 KB per core).</li> <li>Each SC140 core provides the following:</li> <li>Up to 2000 MMACS using an internal 500 MHz clock. A MAC operation includes a multiply-accumulate command with the associated data move and pointer update.</li> <li>4 ALUs per SC140 core.</li> <li>16 data registers, 40 bits each.</li> <li>27 address registers, 32 bits each.</li> <li>Hardware support for fractional and integer data types.</li> <li>Very rich 16-bit wide orthogonal instruction set.</li> <li>Up to six instructions executed in a single clock cycle.</li> <li>Variable-length execution set (VLES) that can be optimized for code density and performance.</li> <li>IEEE® Std 1149.1<sup>™</sup> JTAG port.</li> <li>Enhanced on-device emulation (EOnCE) with real-time debugging capabilities.</li> </ul> |

MSC8122 Product Brief, Rev. 6

| Feature                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Extended Core                            | <ul> <li>Each SC140 core is embedded within an extended core that provides the following:</li> <li>224 KB M1 memory that is accessed by the SC140 core with zero wait states.</li> <li>Support for atomic accesses to the M1 memory.</li> <li>16 KB instruction cache, 16 ways.</li> <li>A four-entry write buffer that frees the SC140 core from waiting for a write access to finish.</li> <li>External cache support by asserting the global signal (GBL) when predefined memory banks are accessed.</li> <li>Programmable interrupt controller (PIC).</li> <li>Local interrupt controller (LIC).</li> </ul>                                                                                                                                                                                                                                                                |

| Multi-Core Shared<br>Memories            | <ul> <li>475 KB M2 memory (shared memory) working at the core frequency, accessible from the local bus, and accessible from all four SC140 cores using the MQBus.</li> <li>4 KB bootstrap ROM.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| M2-Accessible Multi-<br>Core Bus (MQBus) | <ul> <li>A QBus protocol multi-master bus connecting the four SC140 cores to the M2 memory.</li> <li>Data bus access of up to 128-bit read and up to 64-bit write.</li> <li>Operation at the SC140 core frequency.</li> <li>A central efficient round-robin arbiter controlling SC140 core access on the MQBus.</li> <li>Atomic operation control of access to M2 memory by the four SC140 cores and the local bus.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Internal PLL                             | <ul> <li>Generates up to 500 MHz core clock and up to 166 MHz bus clocks for the 60x-compatible local and system buses and other modules.</li> <li>PLL values are determined at reset based on configuration signal values.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 60x-Compatible<br>System Bus             | <ul> <li>64/32-bit data and 32-bit address 60x bus.</li> <li>Support for multiple-master designs.</li> <li>Four-beat burst transfers (eight-beat in 32-bit wide mode).</li> <li>Port size of 64, 32, 16, and 8 controlled by the internal memory controller.</li> <li>Bus can access external memory expansion or off-device peripherals, or it can enable an external host device to access internal resources.</li> <li>Slave support, direct access by an external host to internal resources including the M1 and M2 memories.</li> <li>On-device arbitration between up to four master devices.</li> </ul>                                                                                                                                                                                                                                                                |

| Direct Slave<br>Interface (DSI)          | <ul> <li>A 32/64-bit wide slave host interface that operates only as a slave device under the control of an external host processor.</li> <li>21–25 bit address, 32/64-bit data.</li> <li>Direct access by an external host to internal and external resources, including the M1 and the M2 memories as well as external devices on the system bus.</li> <li>Synchronous and asynchronous accesses, with burst capability in the synchronous mode.</li> <li>Dual or Single strobe modes.</li> <li>Write and read buffers improve host bandwidth.</li> <li>Byte enable signals enables 1, 2, 4, and 8 byte write access granularity.</li> <li>Sliding window mode enables access with reduced number of address pins.</li> <li>Chip ID decoding enables using one CS signal for multiple DSPs.</li> <li>Big-endian, little-endian, and munged little-endian support.</li> </ul> |

| 3-Mode Signal<br>Multiplexing            | <ul> <li>64-bit DSI, 32-bit system bus.</li> <li>32-bit DSI, 64-bit system bus.</li> <li>32-bit DSI, 32-bit system bus, and Ethernet (MII/RMII).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

### Features

| Feature                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory Controller                   | <ul> <li>Flexible eight-bank memory controller:</li> <li>Three user-programmable machines (UPMs), general-purpose chip-select machine (GPCM), and a page-mode SDRAM machine.</li> <li>Glueless interface to SRAM, 166 MHz page mode SDRAM, DRAM, EPROM, Flash memory, and other user-definable peripherals.</li> <li>Byte enables for either 64-bit or 32-bit bus width mode.</li> <li>Eight external memory banks (banks 0–7). Two additional memory banks (banks 9, 11) control IPBus peripherals and internal memories. Each bank has the following features: <ul> <li>32-bit address decoding with programmable mask.</li> <li>Variable block sizes (32 KB to 4 GB).</li> <li>Selectable memory controller machine.</li> <li>Two types of data errors check/correction: normal odd/even parity and read-modify-write (RMW) odd/even parity for single accesses.</li> <li>Write-protection capability.</li> <li>Control signal generation machine selection on a per-bank basis.</li> <li>Support for internal or external masters on the system bus.</li> <li>Data buffer controls activated on a per-bank basis.</li> <li>RMW data parity check (on system bus only).</li> <li>Extensive external memory-controller/bus-slave support.</li> <li>Parity byte select pin, which enables a fast, glueless connection to RMW-parity devices (on the system bus only).</li> <li>Data pipeline to reduce data set-up time for synchronous devices.</li> </ul></li></ul>                                                                                                                                                                                                                                                                             |

| Multi-Channel DMA<br>Controller     | <ul> <li>Data pipeline to reduce data servep time for synchronous devices.</li> <li>16 time-multiplexed unidirectional channels.</li> <li>Services up to four external peripherals.</li> <li>Supports DONE or DRACK protocol on two external peripherals.</li> <li>Each channel group services 16 internal requests generated by eight internal FIFOs. Each FIFO generates: <ul> <li>A watermark request to indicate that the FIFO contains data for the DMA to empty and write to the destination.</li> <li>A hungry request to indicate that the FIFO can accept more data.</li> </ul> </li> <li>Priority-based time-multiplexing between channels using 16 internal priority levels.</li> <li>Round-robin time-multiplexing between channels.</li> <li>A flexible channel configuration: <ul> <li>All channels support all features.</li> <li>All channels connect to the system bus or local bus.</li> </ul> </li> <li>Flyby transfers in which a single data access is transferred directly from the source to the destination without using a DMA FIFO.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Time-Division<br>Multiplexing (TDM) | <ul> <li>Up to four independent TDM modules, each with the following features:</li> <li>Optional operating configurations: <ul> <li>Totally independent receive and transmit channels, each having one data line, one clock line, and one frame sync line.</li> <li>Four data lines with one clock and one frame sync shared among the transmit and receive lines.</li> </ul> </li> <li>Glueless interface to E1/T1 framers and MVIP, SCAS, and H.110 buses.</li> <li>Hardware A-law/µ-law conversion.</li> <li>Up to 62.5 Mbps per TDM for 400/500 MHz core operation; up to 50 Mbps per TDM for 300 MHz core.</li> <li>Up to 256 channels.</li> <li>Up to 16 MB per channel buffer (granularity 8 bytes), where A/µ law buffer size is double (granularity 16 byte).</li> <li>Receive buffers share one global write offset pointer that is written to the same offset relative to their start address.</li> <li>Transmit buffers share one global read offset pointer that is read from the same offset relative to their start address.</li> <li>All channels share the same word size.</li> <li>Two programmable receive and two programmable transmit threshold levels with interrupt generation that can be used, for example, to implement double buffering.</li> <li>Each channel can be programmed to be active or inactive.</li> <li>2-, 4-, 8-, or 16-bit channels are stored in the internal memory as 2-, 4-, 8-, or 16-bit channels, respectively.</li> <li>The TDM Transmitter Sync Signal (TxTSYN) can be configured as either input or output.</li> <li>Frame Sync can be programmed as active low or active high.</li> <li>Selectable delay (0-3 bits) between the Frame Sync signal and the beginning of the frame.</li> </ul> |

MSC8122 Product Brief, Rev. 6

| Feature             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ethernet Controller | Description                • Designed to comply with IEEE Sid 802@ including IEEE Sid. 802.31 <sup>™</sup> , 802.31 <sup>™</sup> , 802.31 <sup>™</sup> , 802.31 <sup>™</sup> , and 802.3ac <sup>™</sup> .                 • 10/100 Mbps MII.             • 10/100 Mbps SMII.                 • 10/100 Mbps SMII.                 • Full-duplex support.                 • Full-duplex flow control (automatic PAUSE frame generation or software programmed PAUSE frame generation and recognition).                 • Support of out-of-sequence transmit queue (for initiating flow-control).                 • Programmable maximum frame length supports jumbo frames (up to 9.6k) and virtual local area network (VLAN) tags and priority.                 • Retransmission from transmit FIPO following a collision.                 • CRC generation and verification of inbound/outbound packets.                 • Address recognition:                 • Each exact match can be programmed to be accepted or rejected.                 • Bratem matching:                 • Hash (256-bit hash) check of group (multicast) addresses.                 • Promiscuous mode.                 • Patterm matching:                 • Up to 16 unique 4-byte patterns.                 • Prodificat addresses of exact matches.                  • Prodificat a |

### Features

| Feature                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UART                                 | <ul> <li>Two signals for transmit data and receive data.</li> <li>No clock, asynchronous mode.</li> <li>Can be serviced either by the SC140 DSP cores or an external host on the system bus or the DSI.</li> <li>Full-duplex operation.</li> <li>Standard mark/space non-return-to-zero (NRZ) format.</li> <li>13-bit baud rate selection.</li> <li>Programmable 8-bit or 9-bit data format.</li> <li>Separately enabled transmitter and receiver.</li> <li>Programmable transmitter output polarity.</li> <li>Two receiver wake-up methods: <ul> <li>Idle line wake-up.</li> <li>Address mark wake-up.</li> <li>Separate receiver and transmitter interrupt requests.</li> </ul> </li> <li>Eight flags, the first five can generate interrupt request: <ul> <li>Transmission complete.</li> <li>Receiver full.</li> <li>Idle receiver input.</li> <li>Receiver overrun.</li> <li>Noise error.</li> <li>Parity error.</li> </ul> </li> <li>Receiver framing error detection.</li> <li>Hardware parity checking.</li> <li>1/16 bit-time noise detection.</li> <li>Maximum bit rate 6.25 Mbps.</li> </ul> |

| General-Purpose I/O<br>(GPIO) Port   | <ul> <li>32 bidirectional signal lines that either serve the peripherals or act as programmable I/O ports.</li> <li>Each port can be programmed separately to serve up to two dedicated peripherals, and each port supports open-drain output mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| I <sup>2</sup> C Software Module     | <ul><li>Booting from a serial EEPROM.</li><li>Uses GPIO timing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Timers                               | <ul> <li>Two modules of 16 timers each.</li> <li>Cyclic or one-shot.</li> <li>Input clock polarity control.</li> <li>Interrupt request when counting reaches a programmed threshold.</li> <li>Pulse or level interrupts.</li> <li>Dynamically updated programmed threshold.</li> <li>Read counter any time.</li> <li>Watchdog mode for the timers that connect to the device.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Hardware                             | Eight coded hardware semaphores, locked by simple write access without need for read-modify-write mechanism.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Global Interrupt<br>Controller (GIC) | <ul> <li>Consolidation of chip maskable interrupt and non-maskable interrupt sources and routing to INT_OUT, NMI_OUT, and to the cores.</li> <li>Generation of 32 virtual interrupts (eight to each SC140 core) by a simple write access.</li> <li>Generation of virtual NMI (one to each SC140 core) by a simple write access.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Reduced Power<br>Dissipation         | <ul> <li>Low power CMOS design.</li> <li>Separate power supply for internal logic (1.1 or 1.2 V) and I/O (3.3 V).</li> <li>Low-power standby modes.</li> <li>Optimized power management circuitry (instruction-dependent, peripheral-dependent, and mode-dependent).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Packaging                            | <ul> <li>0.8 mm pitch Flip-Chip Plastic Ball-Grid Array (FC-PBGA).</li> <li>431-connection (ball).</li> <li>Lead-free or lead-bearing spheres.</li> <li>20 mm × 20 mm.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Real-Time Operating<br>System (RTOS) | <ul> <li>The real-time operating system (RTOS) fully supports device architecture (multi-core, memory hierarchy, ICache, timers, DMA controller, interrupts, peripherals), as follows:</li> <li>High-performance and deterministic, delivering predictive response time.</li> <li>Optimized to provide low interrupt latency with high data throughput.</li> <li>Preemptive and priority-based multitasking.</li> <li>Fully interrupt/event driven.</li> <li>Small memory footprint.</li> <li>Comprehensive set of APIs.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

MSC8122 Product Brief, Rev. 6

### Features

| Feature                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multi-Core Support            | <ul> <li>One instance of kernel code in all four SC140 cores.</li> <li>Dynamic and static memory allocation from local memory (M1) and shared memory (M2).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Distributed System<br>Support | <ul> <li>Transparent inter-task communications between tasks running inside the SC140 cores and the other tasks running in on-board devices or remote network devices:</li> <li>Messaging mechanism between tasks using mailboxes and semaphores.</li> <li>Networking support; data transfer between tasks running inside and outside the device using networking protocols.</li> <li>Integrated device drivers for such peripherals as TDM, UART, and external buses.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Software Support              | <ul> <li>Task debugging utilities integrated with compilers and vendors.</li> <li>Board support package (BSP) for the application development system (ADS).</li> <li>Integrated development environment (IDE):         <ul> <li>C/C++ compiler with in-line assembly so developers can generate highly optimized DSP code. Translates C/C++ code into parallel fetch sets and maintains high code density.</li> <li>Librarian. User can create libraries for modularity.</li> <li>A collection of C/C++ functions for developer use.</li> <li>Highly efficient linker to produce executables from object code.</li> <li>Seamlessly integrated real-time, non-intrusive multi-mode debugger for debugging highly optimized DSP algorithms. The developer can choose to debug in source code, assembly code, or mixed mode.</li> <li>Device simulation models enable design and simulation before hardware availability.</li> <li>Profiler using a patented binary code instrumentation (BCI) technique helps developers identify program design inefficiencies.</li> <li>Version control. CodeWarrior® includes plug-ins for ClearCase, Visual SourceSafe, and CVS.</li> </ul> </li> </ul> |

| Boot Options                  | <ul> <li>External memory.</li> <li>External host.</li> <li>UART.</li> <li>TDM.</li> <li>I<sup>2</sup>C.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MSC8122ADS                    | <ul> <li>Host debug through single JTAG connector supports both processors.</li> <li>MSC8103 as the MSC8122 host with both devices on the board. The MSC8103 system bus connects to the MSC8122 DSI.</li> <li>Flash memory for stand-alone applications.</li> <li>Communications ports: <ul> <li>10/100Base-T.</li> <li>155 Mbit ATM over Optical.</li> <li>T1/E1 TDM interface.</li> <li>H.110.</li> <li>Voice codec.</li> <li>RS-232.</li> <li>High-density (MICTOR) logic analyzer connectors to monitor MSC8122 signals</li> <li>6U cPCI form factor.</li> </ul> </li> <li>Emulates MSC8122 DSP farm by connecting to three other ADS boards.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## **Product Documentation**

The documents listed in **Table 1** are required for a complete description of the MSC8122 and are necessary to design properly with the part. Documentation is available from a local Freescale distributor, a Freescale semiconductor sales office, or a Freescale Literature Distribution Center. For documentation updates, visit the Freescale DSP website. See the contact information on the back of this document.

| Name                               | Description                                                                                                             | Order Number                       |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| MSC8122<br>Technical Data          | MSC8122 features list and physical, electrical, timing, and package specifications                                      | MSC8122                            |

| MSC8122<br>User's Guide            | User information includes system functionality, getting started, and programming topics                                 | MSC8122UG                          |

| MSC8122<br>Reference Manual        | Detailed functional description of the MSC8122 memory and peripheral configuration, operation, and register programming | MSC8122RM                          |

| SC140 DSP Core Reference<br>Manual | Detailed description of the SC140 family processor core and instruction set                                             | MNSC140CORE                        |

| Application Notes                  | Documents describing specific applications or optimized device operation including code examples                        | Refer to the MSC8122 product page. |

| Table 1. MSC8122 Documentatio |

|-------------------------------|

|-------------------------------|

### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

### USA/Europe or Locations not listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GMBH **Technical Information Center** Schatzbogen 7 81829 München, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. **Technical Information Center** 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T. Hong Kong +800 2666 8080 support.asia@freescale.com

For Literature Requests Only: Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

MSC8122PB Rev. 6 4/2005

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale, the Freescale logo, and CodeWarriorare trademarks of Freescale Semiconductor, Inc. StarCore is a trademark of StarCore LLC. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2004, 2005.