# 10MHz - 50GHz High Gain Power Amplifier

#### **Features**

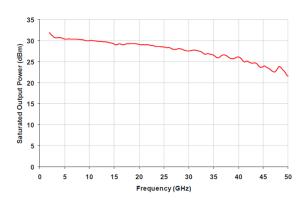

- 30dBm output power @ 10GHz

- 26dBm output power @ 40GHz

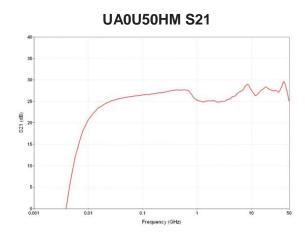

- 28dB gain to 26GHz

- 25dB gain to 40GHz

- Useful gain and power to 50GHz

- Optional integrated power detector

- Small Size

- ECCN 3A001.b.4.c

### **Description**

The UA0U50HM Amplifier is a broadband, high power, moderate gain instrumentation grade amplifier. The amplifier was designed to provide exceptional gain flatness per octave over greater than 5 octaves of frequency coverage. The 10 MHz to 50 GHz amplifier provides up to 30dB of gain

and 30dBm output power with low harmonics and low residual phase noise. The amplifier is provided in a small modular package.

### **Application**

The UA0U50HM Amplifier is an ideal selection for laboratory and instrumentation systems where a high performance broadband RF power amplifier is required. Examples include use as a post amplifier for synthesizers, mixers, modulators, etc. where output powers are low and need to be increased to the 20 dBm to 30 dBm range. The amplifier was designed for use in communications systems, test equipment, military systems, etc.

**Key Characteristics** @  $25^{\circ}$ C: VD1 = VD2 = 6V; VD3 = 7V; Vg1 = Vg2 = Vg3 = -0.1V; Zo =  $50\Omega$

| Parameter  | Description            | 10MHz-<br>2GHz Typ | 2-10GHz<br>Typ | 10-26GHz<br>Typ | 26-40GHz<br>Typ | 40-50GHz<br>Typ |

|------------|------------------------|--------------------|----------------|-----------------|-----------------|-----------------|

| Psat (dBm) | Saturated Output Power | 24                 | 30             | 29              | 27              | 24              |

| P1dB (dBm) | 1db Compressed Power   | 22                 | 28             | 27              | 25              | 22              |

| S21 (dB)   | Small Signal Gain      | 25                 | 29             | 28              | 25              | 24              |

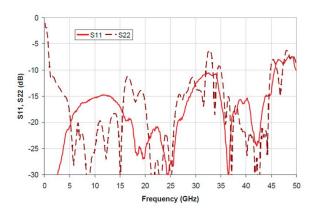

| S11 (dB)   | Input Match            | -15                | -15            | -15             | -10             | -8              |

| S22 (dB)   | Output Match           | -6                 | -15            | -10             | -6              | -6              |

| S12 (dB)   | Reverse Isolation      | -60                | -60            | -60             | -50             | -50             |

| NF (dB)    | Noise Figure           | -                  | 9              | 9               | 10.5            | 12              |

| H2 (dBc)   | 2nd Harmonic @P-1      | -40                | -40            | -40             | -35             | -30             |

| H3 (dBc)   | 3rd Harmonic @P-1      | -20                | -20            | -20             | -               | -               |

## **Absolute Maximum Ratings\***

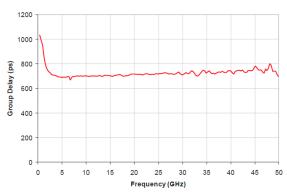

# UA0U50HM Group Delay

### **UA0U50HM S11, S22**

### **UA0U50HM Saturated Output Power**

| Parameter | Description               | Minimum | Тур       | Maximum |

|-----------|---------------------------|---------|-----------|---------|

| Vd1 (V)   | Drain Bias Voltage FET1   | -       | 6         | 8       |

| Vg1 (V)   | Gate Bias Voltage FET1    | -4      | -0.2 to 0 | 0.5     |

| ldd1 (mA) | Drain Bias Current FET1   | -       | 200mA     | 500mA   |

| Vd2 (V)   | Dain Bias Voltage FET2    | -       | 6         | 8       |

| Vg2 (V)   | Gate Bias Voltage FET2    | -4      | -0.2 to 0 | 0.5     |

| ldd2      | Drain Bias Current FET2   | -       | 600mA     | 1000mA  |

| Vd3 (V)   | Drain Bias Voltage FET3   | -       | 7         | 8       |

| Vg3 (V)   | Gate Bias Voltage FET3    | -4      | -0.2 to 0 | 0.5     |

| Idd3 (V)  | Drain Bias Current FET3   | -       | 1000mA    | 1200mA  |

| Pin       | Input Power (CW)          | -       | -         | 20 dBm  |

| Pdc       | Power Dissipation         | -       | 12        | -       |

| Tbs       | Backside Case Temperature | -       | -         | 75°C    |

#### Note:

It is recommended to apply gate bias voltages before drain bias voltages, however, it is not necessary to absolutely guarantee this sequence. This device is robust and will survive drain voltages being applied before gate voltages.

1 Operation listed under the Supplemental Specifications may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Operating Specifications is not implied. Prolonged use at the absolute maximum rating conditions may affect device reliability.

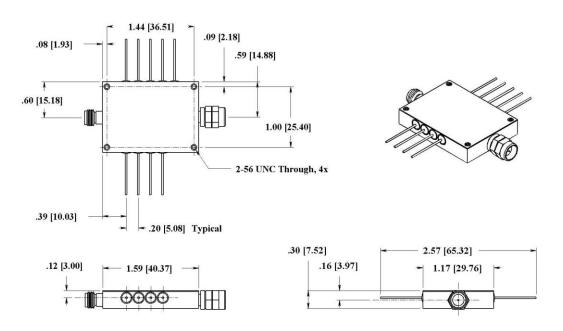

# **Physical Dimensions and Pin Assignment**

# Physical Characteristics

(all measurements in inches[mm])

Tolerance typically +/- 0.0025in (+/- 0.0635mm)

DC pin diameter is 0.03in [0.76mm]

Note: physical dimensions drawing is shown with option 263 (male output V-connector). Standard product is female input V-connector and female output V-connector.

| Pin   | Function                       | Operational Notes                                                      |  |  |

|-------|--------------------------------|------------------------------------------------------------------------|--|--|

| RFin  | RF input                       | V-connector (female)                                                   |  |  |

| RFout | RF output                      | V-connector (female)                                                   |  |  |

| Vg1   | 1st stage gate bias            | Set at typical operating specification                                 |  |  |

| Vg2   | 2nd stage gate bias            | Set at typical operating specification                                 |  |  |

| Vg3   | 3rd stage gate bias            | Set at typical operating specification                                 |  |  |

| Vd1   | 1st stage drain bias           | Set at typical operating specification                                 |  |  |

| Vd2   | 2nd stage drain bias           | Set at typical operating specification                                 |  |  |

| Vd3   | 3rd stage drain bias           | Set at typical operating specification                                 |  |  |

| Ref   | DC reference offset (optional) | Remove this offset from the detector voltage (see appnote AN02)        |  |  |

| Det   | RF power detector (optional)   | Remove the DC offset from this signal and linearize (see appnote AN02) |  |  |

| Gnd   | Connected                      | Connected to Ground                                                    |  |  |

Bias Recommendations (in order):

1) Set gate bias to recommended values; 2) Apply Bias Drains; 3) Adjust bias for optimum gain (maximum gm)

Versatile Bias Board (TE1B) Available. Please visit our website for more information

Information contained in this document is proprietary to Microsem. This document may not be modified in any way without the express written consent of Microsemi. Product processing does not necessarily include testing of all parameters. Microsemi reserves the right to change the configuration and performance of the product and to discontinue product at any time.

#### Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace, and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs, and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at www.microsemi.com.

© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.